## Dynamically Adaptive Header Generator and Front-End Source Emulator for a 100 Gbps FPGA based DAQ

Srikanth Sridharan srikanth.sridharan@cern.ch Marie Curie Fellow: Intel-CERN Doctorate Industrial Program†

The Grand Challenge for proposed upgrade of LHCb experiment:

- 500 Data sources each generating data at 100 Gbps.

- Requires an FPGA DAQ module that

- ▶ handles data generated by the experiment ▶ dynamically adapt to potential inadequacies of other components

- ▶ maintain real time operation while at the same time maintaining system stability and overall data integrity

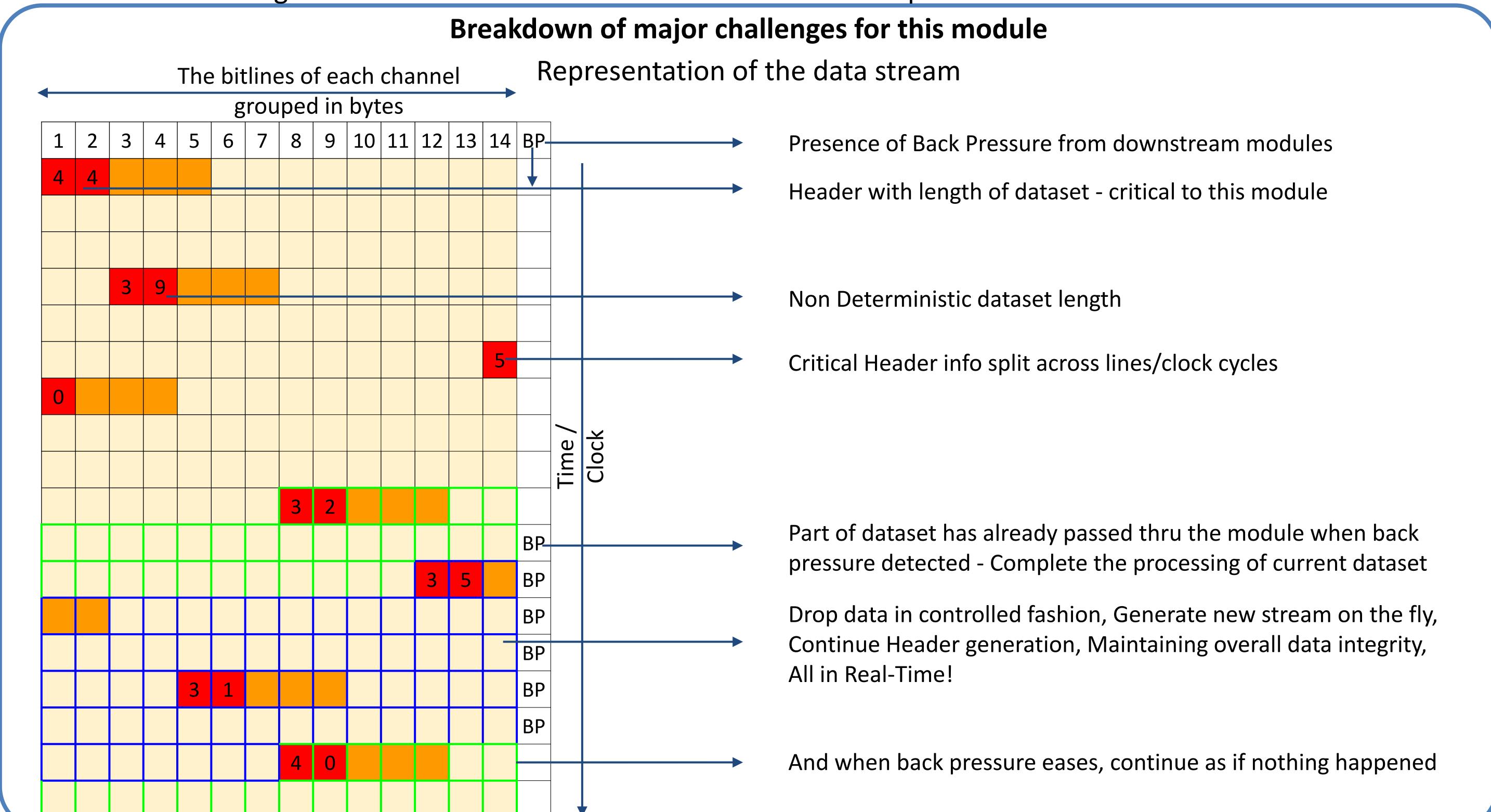

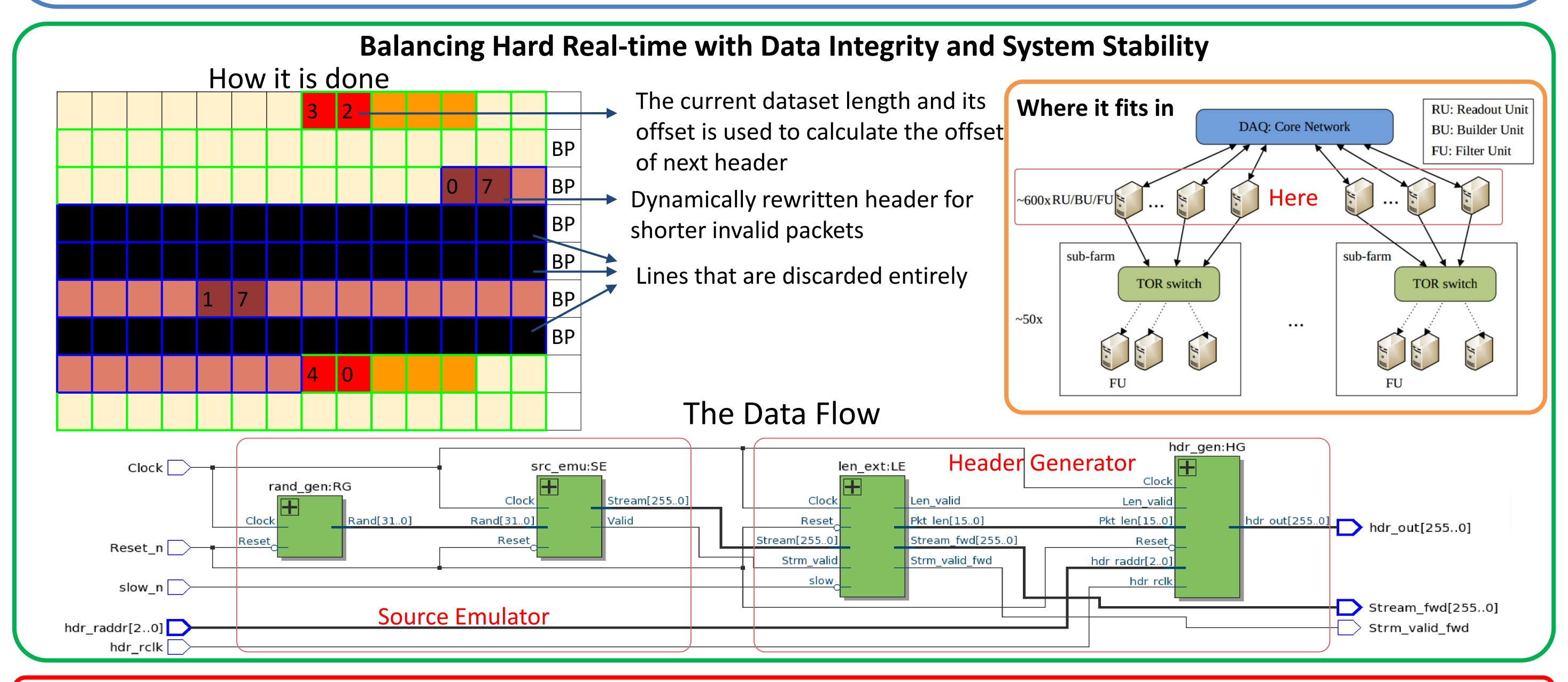

**The Header Generator** module is used to packetize the streaming data from the detector's Front-End electronics before it is sent to the PCs for further processing. The objective is to create a meta header or an index by creating packets out of 100s of small event dataset. This Header contains the total length of the packet, i.e. the sum of lengths of the individual datasets, the length of the largest dataset and a few other details calculated from information in the stream.

The Source Emulator generates the data stream that becomes the test input for Header Generator.